「最近のスマホ、なんでこんなに高いの?」と感じていませんか。

その背景には、3nmから2nmへと進む最先端半導体の進化があります。2026年、スマートフォンの頭脳であるチップは“オングストローム時代”に突入し、構造そのものが大きく変わろうとしています。

消費電力は最大30%削減、オンデバイス生成AIはさらに高速化。一方で、2nmウェハ価格は1枚3万ドル規模ともいわれ、フラッグシップ機は20万円超えが現実味を帯びています。

本記事では、FinFETからGAAへの転換、TSMC・Samsung・Intelの三つ巴競争、日本のRapidusの現在地、そしてiPhone 18やGalaxy S26がどう変わるのかまで、ライトユーザーにもわかりやすく整理します。

「結局、買い替えるべき?」という疑問に答えられるよう、価格と性能のバランスも含めて徹底解説します。

- なぜ今「2nm」が話題なのか?ムーアの法則とオングストローム時代の到来

- 3nmと2nmの決定的な違い──FinFETからGAA(全周ゲート)への構造転換

- 裏面電源供給(BSPDN)とは?電力効率と発熱を左右する新技術

- TSMC・Samsung・Intelの三つ巴競争と2nm覇権の行方

- Rapidusは本当に成功するのか?千歳から始まる日本半導体再興

- iPhone 18・Galaxy S26はどう変わる?次世代SoCの進化ポイント

- 20万円スマホ時代は本当?2nm移行がもたらす価格への影響

- オンデバイスAIとバッテリー革命──ユーザー体験はどこまで進化するか

- 冷却技術の進化:ベイパーチャンバーと新パッケージングの重要性

- 参考文献

なぜ今「2nm」が話題なのか?ムーアの法則とオングストローム時代の到来

いまテック業界で「2nm(ナノメートル)」という言葉がこれほど注目されているのは、単なる数字の更新ではないからです。これはムーアの法則が新たな形で延命し、半導体が“オングストローム時代”へ踏み込む入口に立っていることを意味します。

ムーアの法則とは、半導体のトランジスタ数が約2年ごとに倍増するという経験則です。長年にわたりスマートフォンの性能向上やバッテリー持ちの改善を支えてきました。しかし3nm世代に至り、従来のFinFET構造は物理的限界に直面していました。そこで登場したのが2nm世代です。

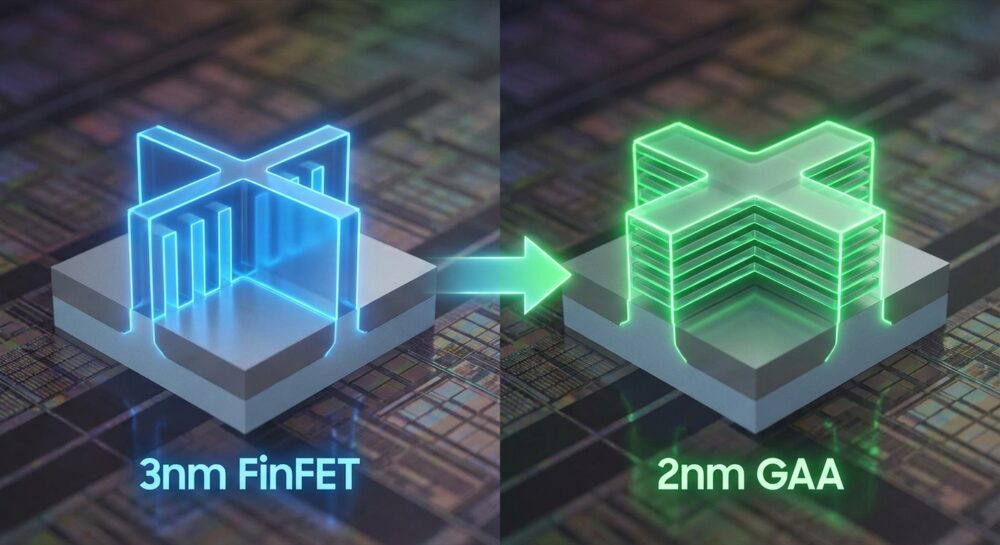

2nmは単なる微細化ではなく、トランジスタ構造そのものの刷新を伴います。FinFETからGAA(Gate-All-Around)へという大転換です。IBM ResearchやSemiWikiの解説によれば、GAAはチャネルを360度ゲートで囲むことでリーク電流を大幅に抑えられます。

| 世代 | 主な構造 | 特徴 |

|---|---|---|

| 3nm | FinFET | 3方向から制御、限界が顕在化 |

| 2nm | GAA(ナノシート) | 360度制御で高効率・低リーク |

TSMCの公開情報では、2nm世代は3nm比で同一性能なら消費電力を25〜30%削減できるとされています。これはライトユーザーにとっては「充電回数が減る」「発熱が抑えられる」という体感的な違いにつながります。

さらに注目すべきは「オングストローム時代」という言葉です。1nmは10オングストロームに相当します。つまり2nmは20オングストローム級。すでに業界ではIntelの18A(1.8nm相当)など、ナノメートルよりさらに細かい単位を意識したネーミングが登場しています。

ムーアの法則は終わったと何度も言われてきました。しかし実際には、構造を変え、電源供給方法を見直し、パッケージ技術を進化させることで前進を続けています。McKinsey Electronicsも、こうした革新が次世代AI処理の前提条件だと指摘しています。

なぜ今2nmが話題なのか。それはスマートフォンの進化が「速くなる」から「賢くなる」段階へ移る分岐点だからです。オンデバイスAIの高度化、長時間駆動、そして発熱の抑制。その土台となるのが、この2nm世代なのです。

3nmと2nmの決定的な違い──FinFETからGAA(全周ゲート)への構造転換

3nmと2nmの違いは、単に「数字が1小さくなった」ことではありません。トランジスタの構造そのものが変わるという、歴史的な転換点にあります。

3nm世代まで主流だったのはFinFET(フィンフェット)構造です。これはシリコンをヒレのように立ち上げ、ゲートが3方向から包み込む仕組みでした。22nm世代から導入され、長年にわたり性能向上を支えてきました。

しかし3nm以下になると、ヒレ同士の間隔が極端に狭くなり、電流をうまく止められない「短チャネル効果」が顕在化します。これがFinFETの物理的な限界とされています。

| 項目 | 3nm(FinFET) | 2nm(GAA) |

|---|---|---|

| チャネル形状 | ヒレ状(Fin) | ナノシート積層 |

| ゲートの囲み方 | 3方向 | 360度全周 |

| リーク電流 | 抑制に限界 | 大幅に低減 |

| 設計自由度 | Fin本数で段階調整 | シート幅を連続調整 |

2nm世代で採用されるのがGAA(Gate-All-Around)です。IBM ResearchやSemiWikiの解説によれば、チャネルを水平なナノシートとして積み重ね、それをゲートが四方から完全に包み込む構造です。

これによりオフ時のリーク電流が劇的に減少します。TSMCの説明では、3nm比で25〜30%の消費電力削減が可能とされており、これはスマートフォンの待機電力や常時AI処理に直結します。

もう一つ重要なのが設計の自由度です。FinFETでは性能向上のためにヒレの本数を増やす必要があり、1本、2本と“段階的”にしか調整できませんでした。

一方GAAのナノシートは、シートの幅を連続的に変えられます。高速処理が必要なコアには幅広、省電力重視のコアには幅狭といった最適化が可能です。これはDTCOと呼ばれる設計と製造の協調最適化を大きく前進させます。

実際、TSMCのN2、SamsungのSF2、Intelの18AはいずれもGAA系構造を採用しています。名称はナノシート、MBCFET、RibbonFETと異なりますが、本質は全周ゲートです。

つまり3nmから2nmへの移行は、ムーアの法則を数字で延命したというよりも、トランジスタを再発明した世代交代といった方が正確です。ここから先の性能向上は、この構造転換が土台になっていきます。

裏面電源供給(BSPDN)とは?電力効率と発熱を左右する新技術

裏面電源供給(BSPDN:Backside Power Delivery Network)とは、これまでチップの表側に集まっていた電源配線を、シリコンの裏面に移す新しい設計思想です。

一見すると地味な変更に思えますが、電力効率と発熱を大きく左右するゲームチェンジャーとして注目されています。

2nm世代では、トランジスタそのものだけでなく、電気の通り道まで根本から見直されているのです。

従来構造との違い

| 項目 | 従来(表面給電) | BSPDN |

|---|---|---|

| 電源配線 | 表面に配置 | 裏面に配置 |

| 信号配線との関係 | 混在 | 物理的に分離 |

| 主な課題 | 配線混雑・電圧降下 | 放熱設計の難化 |

従来のチップでは、信号用の細かな配線と、電源用の配線が同じ表面に何層にも重なっていました。

微細化が進むにつれて配線は極細化し、電気抵抗が増大します。その結果、IRドロップと呼ばれる電圧低下や、信号干渉が問題になっていました。

マッキンゼーの半導体分析によれば、先端ノードでは電源供給ネットワークが性能ボトルネックになりつつあると指摘されています。

BSPDNは電源配線を裏面に移し、シリコンを貫通するビアで直接トランジスタへ電力を供給します。

これにより、表面は信号専用に最適化でき、配線密度が向上します。

結果として電力ロスが減り、同じバッテリー容量でもより長く使える可能性が高まります。

実際、Intelは18Aプロセスで「PowerVia」と呼ばれる裏面電源供給を量産導入しました。

業界メディアのTechPowerUpなどによると、ロジック密度や電力効率の面で優位性を示す技術要素のひとつと評価されています。

標準セル利用効率が90%以上に高まるという分析もあり、チップ面積の縮小にもつながります。

ただしメリットだけではありません。

Semiconductor Engineeringが報じているように、トランジスタが上下の配線層に挟まれる構造になるため、熱の逃げ道が複雑になります。

つまり、電力効率は向上しても、放熱設計はより高度になるという新たな課題が生まれます。

スマートフォンでは、この課題に対して大型ベイパーチャンバーや新しいパッケージ技術が組み合わされます。

BSPDNは単体で完結する技術ではなく、冷却設計やパッケージングと一体で初めて真価を発揮します。

見えない裏側の配線変更が、バッテリー持ちや持続性能に直結する――それがこの新技術の面白さです。

TSMC・Samsung・Intelの三つ巴競争と2nm覇権の行方

2nm時代の主役は、TSMC・Samsung・Intelの3社です。かつてはTSMCの独走といわれましたが、2026年はいよいよ本格的な「三つ巴」の構図になっています。

ポイントは、単なる微細化競争ではなく、歩留まり・価格・新技術の導入タイミングという現実的な要素で勝負が分かれていることです。

| 企業 | 主力2nm世代 | 特徴 | 戦略の軸 |

|---|---|---|---|

| TSMC | N2 | GAA採用、BSPDNは次世代 | 安定供給と顧客信頼 |

| Samsung | SF2 | 歩留まり改善(60-70%報道) | 価格競争力と顧客奪還 |

| Intel | 18A | GAA+PowerVia同時導入 | 技術先行で巻き返し |

まずTSMCは、N2でGAA(ナノシート)を採用しつつも、裏面電源供給は見送る堅実路線です。TrendForceやTom’s Hardwareの報道によれば、N2の生産能力はすでに逼迫し、Appleなど主要顧客が確保済みとされています。最先端でも「確実に量産できる」ことが最大の武器です。

一方のSamsungは、3nm世代で苦戦した後、SF2で歩留まりを60〜70%まで改善したと報じられています。Qualcomm向け2nmチップのサンプル出荷も伝えられ、価格面でもTSMCより戦略的に攻める姿勢です。TSMC一強を避けたいファブレス企業にとって、有力な選択肢になりつつあります。

そして最も攻めているのがIntelです。18AではGAA(RibbonFET)と裏面電源供給「PowerVia」を同時に量産導入しました。TechPowerUpなどの分析では、性能クラスで競合を上回る可能性も指摘されています。技術的リーダーシップの奪還が最大の狙いです。

ただし覇権は「技術が最先端か」だけでは決まりません。ウェハ価格は2nmで約3万ドルともいわれ、巨額投資を回収できる受注量が不可欠です。安定供給のTSMC、価格と復活のSamsung、技術先行のIntel。三者三様の戦略がぶつかる中、2nmの真の勝者は2026〜2027年の量産実績で決まります。

スマホユーザーにとっては、その裏側で繰り広げられるこの競争こそが、次世代のバッテリー持ちやAI性能を左右しているのです。

Rapidusは本当に成功するのか?千歳から始まる日本半導体再興

Rapidusは本当に成功するのでしょうか。結論から言えば、技術面では確実に前進しており、あとは量産と顧客獲得が最大の焦点です。

北海道・千歳市に建設されたIIM-1工場では、2025年4月に2nmパイロットラインが稼働しました。さらに同年7月には、GAA(Gate-All-Around)構造の2nmトランジスタの試作と動作確認に成功したと発表しています。

これはIBMとの共同開発の成果であり、2027年量産という目標に向けた重要なマイルストーンです。少なくとも「絵に描いた餅」ではない段階に入っています。

| 項目 | Rapidusの状況 |

|---|---|

| 拠点 | 北海道・千歳市 IIM-1 |

| プロセス | 2nm(GAA採用) |

| パイロット開始 | 2025年4月 |

| 量産目標 | 2027年 |

ただし、成功のハードルは極めて高いです。2nm世代のウェハ価格は1枚あたり約30,000ドルとも報じられており、設備投資額も数兆円規模になります。TSMCやSamsung、Intelといった巨大ファウンドリと同じ土俵で戦うのは簡単ではありません。

そこでRapidusが掲げるのが「RUMS(Rapid and Unified Manufacturing Service)」です。これは大量生産型ではなく、設計から製造までを一体化し、小ロットでも短納期で高付加価値チップを提供するモデルです。

AI向け専用チップやカスタムSoCなど、スピードと柔軟性が求められる分野に特化する戦略といえます。

さらに見逃せないのが、日本企業による強力なサプライチェーンです。東京エレクトロンの最先端塗布現像装置、SCREENの洗浄技術、JSRのEUV向けフォトレジストなど、日本企業は2nm製造の要所を押さえています。

Brookings Institutionも、日本は素材・装置分野で世界的な競争力を持つと指摘しています。Rapidus単体ではなく、エコシステム全体で戦う構図です。

成功の鍵は3つに集約されます。量産時の歩留まり、安定した顧客の確保、そして継続的な資金調達です。特に歩留まりは利益を左右する核心であり、ここでつまずけば事業は成り立ちません。

それでも、2nm試作成功という事実は大きな前進です。千歳から始まった挑戦が、日本半導体再興の象徴になるのかどうか。2027年の量産開始が、その答えを示す分岐点になります。

iPhone 18・Galaxy S26はどう変わる?次世代SoCの進化ポイント

iPhone 18やGalaxy S26で注目されているのが、3nmから2nm世代へと進化する次世代SoCです。今回の進化は単なる「微細化」ではありません。トランジスタ構造そのものが変わる歴史的な転換点にあたります。

これまで主流だったFinFET構造は3nm付近で物理的限界が見え始め、2nm世代ではGAA(Gate-All-Around)構造へ本格移行しています。IBM ResearchやSemiWikiによれば、GAAはチャネルを360度ゲートで囲むことでリーク電流を大幅に抑制できるのが特長です。

その結果、TSMCの公表資料では3nm世代と比べて同一性能で25〜30%の消費電力削減が可能とされています。これはスマホのバッテリー持ちに直結する改善です。

| 項目 | 3nm世代 | 2nm世代 |

|---|---|---|

| トランジスタ構造 | FinFET | GAA(ナノシート等) |

| 電力効率 | 従来比改善 | さらに約25〜30%削減 |

| 設計自由度 | Fin本数で調整 | シート幅を連続的に調整可能 |

特に重要なのは設計の自由度です。GAAではナノシートの幅を細かく調整できるため、高性能コアと省電力コアをより最適化できます。iPhone 18のA20やGalaxy S26向けSoCでは、AI処理用コアと日常動作用コアの効率差がさらに拡大する可能性があります。

もうひとつの進化ポイントが、裏面電源供給(BSPDN)です。Intelは18Aプロセスで「PowerVia」を量産導入すると発表しています。これは電源配線をチップ裏面に回す技術で、表面の信号配線を効率化できます。

McKinsey Electronicsの分析によれば、この方式は電圧降下を抑え、電力効率向上と高クロック安定化に寄与します。今後モバイルSoCにも広がれば、重いAI処理でも発熱を抑えつつ性能を維持しやすくなるでしょう。

さらに見逃せないのが、オンデバイスAIへの最適化です。Qualcommが紹介しているように、クラウドを介さない生成AI処理は低遅延・高プライバシーが強みです。2nm世代ではトランジスタ密度向上によりNPUを大型化しやすくなります。

その結果、リアルタイム翻訳や高度な画像生成、音声アシスタントがより高速かつ安定して動作します。単なるベンチマークの数字ではなく、体感できる「賢さ」と「電池持ち」の両立こそが次世代SoCの最大の進化ポイントです。

iPhone 18とGalaxy S26は、スペック競争の次の段階へ進みます。微細化の数字以上に、構造改革と電力設計の革新が、日常体験そのものを底上げする時代に入ろうとしています。

20万円スマホ時代は本当?2nm移行がもたらす価格への影響

「次のハイエンドは20万円超えが当たり前になるのでは?」そんな声が現実味を帯びてきました。背景にあるのが、3nmから2nmへの移行による製造コストの急上昇です。

半導体業界の分析によれば、TSMCの2nmウェハ価格は1枚あたり約30,000ドルに達すると予測されています。これは5nm世代のおよそ2倍、3nmと比べても大幅な上昇です。

スマホの頭脳であるSoCは、このウェハから切り出されます。つまり、土台のコストが跳ね上がれば、最終製品の価格にも波及するのは避けられません。

| 世代 | 推定ウェハ価格 | 価格インパクト |

|---|---|---|

| 5nm | 約16,000ドル | 基準 |

| 3nm | 約20,000ドル | 上昇傾向 |

| 2nm | 約30,000ドル | 大幅上昇 |

さらに追い打ちをかけるのがメモリ価格です。市場調査では、モバイルDRAMやNANDフラッシュの価格が大きく上昇しており、メモリはスマートフォン製造コストの約2割を占めるとの指摘もあります。

チップ単体のコストも無視できません。一部報道では、2nm世代のA20チップが従来より大幅に高額になる可能性があると伝えられています。仮にSoCコストが数十ドル単位で上がれば、最終価格は1〜2万円では収まりません。

実際、2026年以降のフラッグシップ機は10〜20%程度の価格上昇が見込まれ、ハイエンド帯が20万円〜30万円にシフトする可能性も指摘されています。これは為替や流通コストを含めた総合的な影響です。

ただし、ここで重要なのは「値上げ=企業の利益増」ではない点です。EUV露光装置の増加、GAA構造への移行、歩留まり確保のための投資など、2nmは桁違いの設備投資を必要とします。業界レポートでは、2nm工場の建設費が数百億ドル規模に達するとされています。

つまり、20万円スマホは単なるブランド戦略ではなく、最先端技術のコストをそのまま反映した結果とも言えるのです。今後は「毎年買い替える」から「数年使う前提」へと、ユーザー側の価値観も変わっていくかもしれません。

2nm時代は、性能競争だけでなく価格とのバランスが問われるフェーズに入っています。私たちが支払う金額の裏には、ナノレベルの技術革新と莫大な投資があることを知っておくと、価格の意味も少し違って見えてきます。

オンデバイスAIとバッテリー革命──ユーザー体験はどこまで進化するか

スマートフォンの進化は、いよいよ「手のひらでAIが完結する時代」に入ろうとしています。その鍵を握るのが2nm世代のチップです。TSMCによれば、2nmプロセスは3nm世代と比べて同一性能で消費電力を25〜30%削減できるとされ、これがオンデバイスAIとバッテリー体験を同時に押し上げます。

特に注目したいのは、GAA構造によるリーク電流の大幅な低減です。待機中や軽い操作時の無駄な電力消費が抑えられるため、日常使いでの“じわじわ減る”バッテリーが改善します。モバイル向け半導体の電力効率は体感差に直結し、一般的な利用環境で充電頻度が減る可能性があります。

2nm世代は「高性能化」よりも「賢く長く使える」体験を実現する世代です。

オンデバイスAIの進化も見逃せません。Qualcommはオンデバイス生成AIの利点として、低遅延・高いプライバシー保護・常時利用可能性を挙げています。クラウドに送信せずに画像生成や文章要約、リアルタイム翻訳を処理できるため、通信状況に左右されずスムーズです。

2nm世代ではNPU(AI専用エンジン)の大規模化が可能になります。GAA構造は同じ面積でより多くのトランジスタを効率よく配置できるため、AI処理専用回路を強化しつつ発熱と消費電力を抑えられます。

| 項目 | 3nm世代 | 2nm世代 |

|---|---|---|

| トランジスタ構造 | FinFET | GAA |

| 消費電力効率 | 従来比改善 | さらに25〜30%削減 |

| AI処理 | 一部クラウド依存 | 高度な生成AIを端末内で実行 |

| 待機電力 | リーク課題あり | リーク大幅低減 |

さらに、裏面電源供給技術の導入が進めば、電力供給効率が向上し、同じバッテリー容量でもより長時間の高負荷AI処理が可能になります。McKinseyの分析でも、電源配線を分離することで電圧降下が抑えられ、電力効率が改善すると指摘されています。

もちろん、AI処理が増えれば発熱も増します。しかし近年はベイパーチャンバーなどの冷却技術が標準化しつつあり、持続性能を確保する方向に進んでいます。つまり、写真編集や動画生成を長時間行ってもパフォーマンスが落ちにくくなるのです。

通信に頼らず、バッテリーを気にせず、賢いAIが常にそばにいる。2nm時代のモバイル体験は、単なるスペック向上ではなく、使い方そのものを変える静かな革命といえます。

冷却技術の進化:ベイパーチャンバーと新パッケージングの重要性

2nm世代のチップは、性能と電力効率が大きく向上する一方で、発熱密度もこれまで以上に高まっています。特にGAA構造や高密度化の進展により、同じ面積により多くのトランジスタが詰め込まれるため、熱をいかに効率よく逃がすかがスマートフォン設計の鍵になります。

半導体専門メディアSemiconductor Engineeringによれば、裏面電源供給のような新構造は電力効率を高める一方で、熱設計の難易度を引き上げる側面も指摘されています。つまり、チップが進化するほど、冷却技術も同時に進化しなければならないのです。

そこで注目されているのがベイパーチャンバーです。ベイパーチャンバーは内部に封入された液体が蒸発・凝縮を繰り返すことで熱を拡散する仕組みで、従来のグラファイトシートよりも効率よく熱を広い面積に逃がせます。

DIGITIMESの報道では、Appleが次世代iPhone向けに独自設計のベイパーチャンバーを採用する動きが伝えられています。また、Galaxy S26 Ultraではベイパーチャンバーの面積を前世代比で1.2〜1.5倍に拡大する設計が検討されていると報じられています。

| 冷却方式 | 特徴 | 主なメリット |

|---|---|---|

| グラファイトシート | 薄型で軽量 | コストが低く量産向き |

| ベイパーチャンバー | 相変化で熱を拡散 | 高負荷時の温度上昇を抑制 |

| FOWLP-HPB | パッケージ内に放熱経路 | チップ直上から効率的に放熱 |

さらに重要なのがパッケージング技術との融合です。Samsungが採用を進めるFOWLP-HPBは、チップ直上に放熱経路を設けることで熱抵抗を下げ、持続的な高クロック動作を可能にする設計です。これは単なる外付け冷却ではなく、半導体パッケージそのものに熱対策を組み込む発想です。

TSMCのCoWoSやSoIC、IntelのFoverosといった3D実装技術も、チップとメモリを近接配置することで性能を引き上げる一方、熱集中という課題を生みます。そのため、パッケージレベルでの熱拡散設計は今後さらに重要になります。

結果として、冷却性能の差が「ベンチマークスコア」だけでなく「長時間ゲームやAI処理での安定性」に直結します。スペックが同じでも、冷却設計が優れているモデルの方がパフォーマンスを維持しやすいのです。

2nm時代のスマートフォン選びでは、チップ名だけでなく、ベイパーチャンバーの有無やパッケージング技術といった“見えない冷却力”にも注目することが、賢い選択につながります。

参考文献

- Tom’s Hardware:TSMC’s 2nm process will reportedly get another price hike — $30,000 per wafer for latest cutting-edge tech

- SemiWiki:GAAFET (Gate-All-Around FET) Wiki

- McKinsey Electronics:Backside Power Delivery | Boosting 2nm Chips & AI Performance

- TechPowerUp:Intel’s 18A Node Outperforms TSMC N2 and Samsung SF2 in 2 nm Performance Class

- JAPAN Forward:Rapidus Ushers in New Era with Operational 2nm Chip Prototype

- Wccftech:Mobile DRAM, NAND Flash Prices Have Risen By More Than 70% And 100%, Respectively

- Qualcomm:5 benefits of on-device generative AI